# CSc 360 Operating Systems Review

### Jianping Pan Summer 2006

5/3/06 CSc 360

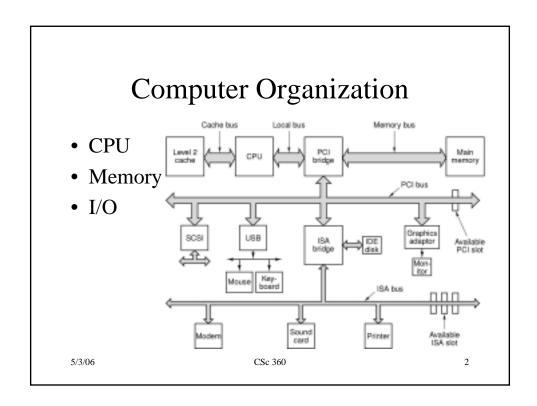

### **CPU**

- Access

- pins: address, data, control, status

- Internals

- program counter (PC)

- registers: address, data, control, flags

- arithmetic logic unit (ALU), FPU, etc

- Benchmarks

- clock (GHz), instruction/cycle, MIPS

%/06 CSc 360

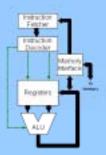

## **CPU** operations

- Fetch

- retrieve instructions from memory (cache)

- Decode

- instruction: operator, operands; microcode

- Execute

- arithmetic/logic operation

- move data between register, memory, I/O

- change execution flow

3/06 CSc 360

### Memory

- Access

- linear address

- segmented address: segment, index

- physical address: cylinder, header, sector (disk)

- Benchmarks

- clock (MHz)

- width (bits)

- throughput (Mbps)

5/3/06 CSc 360

## Memory hierarchies

- Speed vs. size (vs. cost)

- registers: inside CPU

- cache: transparent to programs

- memory: main storage

- DRAM, SDRAM, SRAM, etc

- disks: secondary storage

- electronic, magnetic, optical, etc

- tapes: backup storage

<sub>5/3/06</sub> – networked storage <sub>CSc 360</sub>

6

### I/O

- A large variety of input/output devices

- keyboard/mouse, video, audio, network, etc

- Access

- Address

- port numbers

- I/O vs. memory space

- Interrupt

- Direct memory access (DMA)

5/3/06 CSc 360

### Interrupts

- Asynchronous operation

- Nonmaskable interrupts

- e.g., hardware fault

- Hardware interrupts

- hardware events: e.g., I/O completion

- interrupt controller: priority & arbitration

- Software interrupts

- trap, system call

5 CSc 360

8

### Interrupt handling

- Save current state

- CPU counters, registers, flags at system stack

- Update program counter

- interrupt controller; interrupt vectors

- Execute interrupt routine

- Restore previous state

- Multiple interrupts

priority, masking, reentry

9

10

### **DMA**

- High-speed I/O, bulk data transfer

- DMA controller

- source/destination address

- counter: the amount of data to be moved

- DMA handling

- program DMA controller

- execute DMA concurrently

- issue an interrupt on DMA completion

5/3/06 CSc 360

## Computer architectures

- Single-processor systems

- Multi-processor systems

- symmetric multiprocessing (SMP)

- Cluster systems

- interconnected systems

- Distributed systems

- networked systems

- ullet Grid systems

CSc 360

11

### This lecture

- Review computer organization and computer architecture

- CPU, memory, I/O, interrupt, DMA

- multiprocessor, cluster, distributed, grid

- Explore further

- $\ Linux \ with \ /proc$

- cpuinfo, meminfo, iomem, ioports, interrupts, dma

5/3/06 CSc 360 12

# Next lecture

- An overview on operating systems

- read OSC Chapter 1

5/3/06 CSc 360 13